电子Chiplet:提质增效,助力国产半导体弯道超车中泰证券2023-03-27.pdf

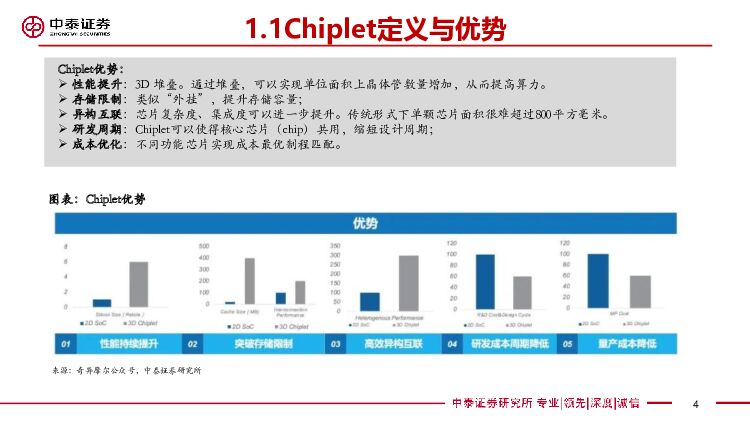

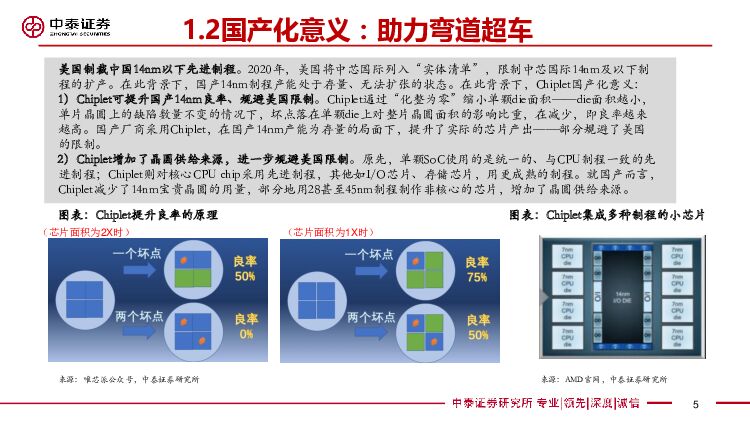

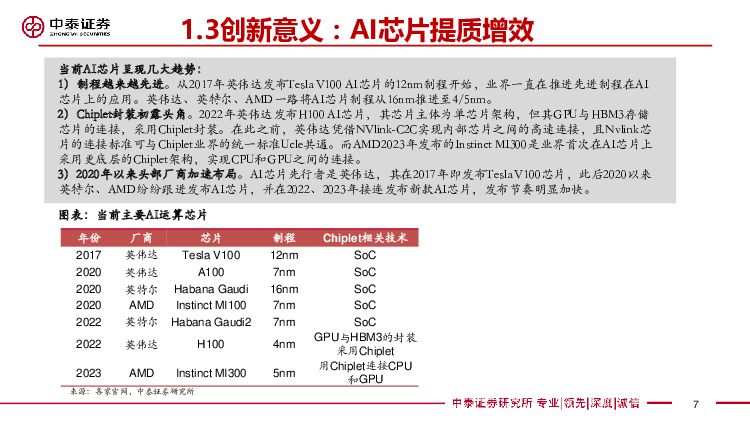

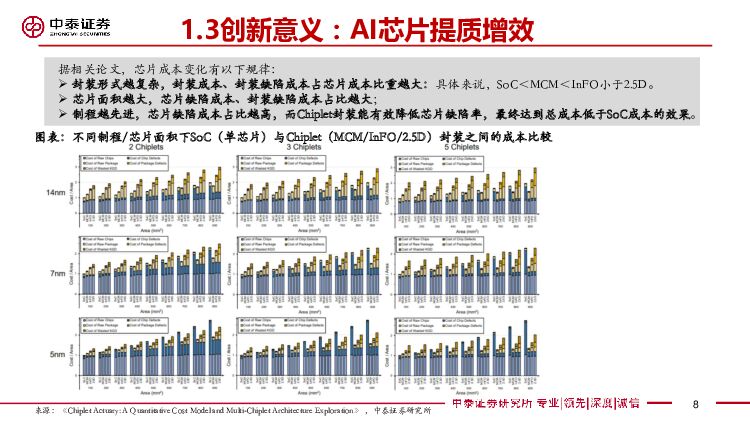

摘要:Chiplet定义:将单颗SoC“化整为零”为多颗小芯片(Chip),将多颗Chips进行封装的技术。可分为:1)MCM:Multi-ChipModule,多芯片组件。MCM将多颗裸芯片连接于同一块基板(陶瓷、硅、金属基板),并封装到同一外壳。往下可细分为金字塔堆叠MCM和TSV(硅通孔)堆叠MCM。2)InFO:IntegratedFan-Out,集成扇出封装。InFO指集成多颗进行扇出型封装,所谓扇出(Fan-Out),指Die表面的触点扩展到Die的覆盖面积之外,增加了凸点布置的灵活性并增多了引脚数量。InFO与MCM的区别在于InFO强调扇出封装。3)2.5DCoWoS:ChiponWaferonSubstrate,即从上往下为小芯片-interposer(转接板,硅wafer或其他材料)-IC载板。其与InFO区别在于,2.5DCoWoS多了一层interposer,InFO通常无interposer。需注意,以上三种封装并无严格界限,其区别在于每一种形式侧重的封装要素不同。Chiplet优势:性能提升:3D堆叠。通过堆叠,可以实现单位面积上晶体管数量增加,从而提高算力。存储限制:类似“外挂”,提升存储容量;异构互联:芯片复杂度、集成度可以进一步提升。传统形式下单颗芯片面积很难超过800平方毫米。研发周期:Chiplet可以使得核心芯片(chip)共用,缩短设计周期;成本优化:不同功能芯片实现成本最优制程匹配。

免责声明: 1.本站部分作品是由网友自主投稿和发布、编辑整理上传,对此类作品本站仅提供交流平台,不为其版权负责。 2.如发布机构认为违背了您的权益,请与我们联系,我们将对相关资料予以删除。 3.资源付费,仅为我们搜集整理和运营维护费用,感谢您的支持!

合集服务: 单个细分行业的合集获取请联系行研君:hanyanjun830

-

【中泰汽车】低空经济专题报告:值得重视的新质生产力代表—元年或至 中泰证券 2024-04-18(32页) 附下载

核心观点为什么低空经济本轮值得重视?1)政策支撑—顶层设计,自上而下:低空经济是战略新兴产业和新质生...

7.76 MB共32页中文简体

1天前020积分

-

【中泰汽车·整车行业格局系列深度研究(2)】北京车展前瞻:基于优质细分车格筛选方法论筛选重点车型 中泰证券 2024-04-18(57页) 附下载

北京车展:市场关注度高,但缺少定量判断各家新车布局的研究方法论目前市场对于北京车展保持高关注度但缺少...

3.41 MB共57页中文简体

1天前020积分

-

消费电子行业研究周报:各大厂商加快芯片开发,持续看好算力投资 天风证券 2024-04-18(27页) 附下载

AI:谷歌2024年度云会议:谷歌在其云端AI基础设施中引入了基于Arm的Axion CPU,推出了...

2.09 MB共27页中文简体

1天前220积分

-

产业演进视角看“消费降级”:买方时代,零售、品牌结构重塑 中泰证券 2024-04-18(23页) 附下载

投资要点核心观点:市场热议的“消费降级”有经济周期的影响,但更重要的原因是商品、零售商走向过剩,消费...

1.07 MB共23页中文简体

1天前020积分

-

兴瑞科技 汽车电子业务助推业绩成长,新能源汽零基地投产在即 国投证券 2024-04-18(5页) 附下载

兴瑞科技(002937)事件:公司发布2023年年度报告,全年实现营收20.06亿元,同比增长13....

960.27 KB共5页中文简体

1天前018积分

-

兴瑞科技 2023年报点评:汽车电子业务超预期高增,看好汽车电装业务长期成长 东吴证券 2024-04-18(3页) 附下载

兴瑞科技(002937)事件:公司发布2023年报整体业绩符合市场预期,汽车电子业务实现高增:202...

524.78 KB共3页中文简体

1天前218积分

-

新大正 收入稳健增长,多重因素致利润下行 中泰证券 2024-04-18(3页) 附下载

新大正(002968)投资要点新大正发布2023年年报,公司2023年实现营收31.27亿,同比+2...

499.4 KB共3页中文简体

1天前218积分

-

新澳股份 业绩符合预期,销量增长稳健,羊绒盈利能力提升 中泰证券 2024-04-18(5页) 附下载

新澳股份(603889)投资要点事件:披露23年报,业绩符合预期,扣非利润增长稳健。23年实现营业收...

477.13 KB共5页中文简体

1天前318积分

-

龙迅股份 单季度收入再创新高,汽车电子新品持续拓展 国金证券 2024-04-18(4页) 附下载

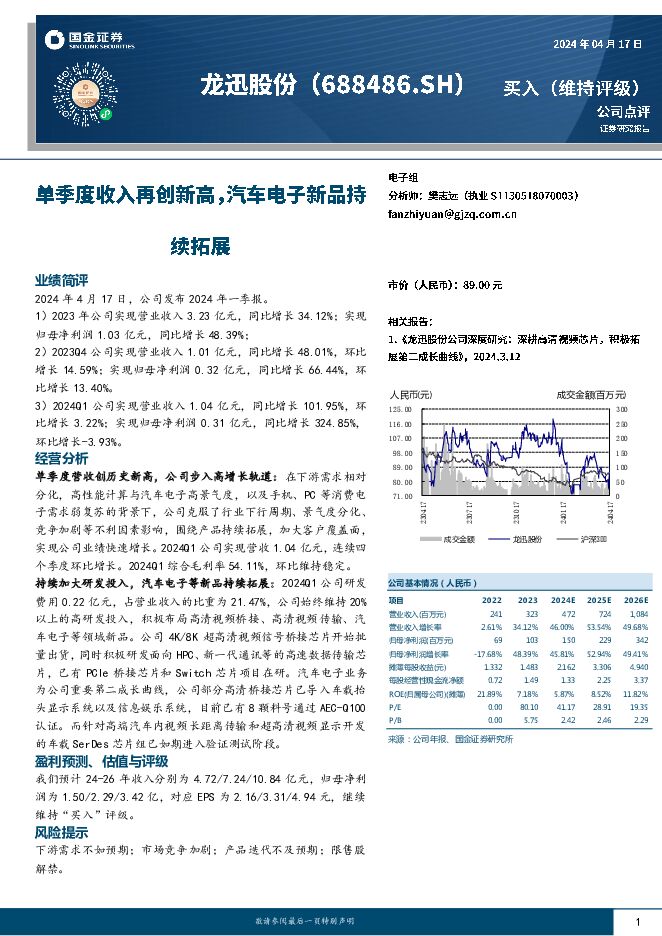

龙迅股份(688486)业绩简评2024年4月17日,公司发布2024年一季报。1)2023年公司实...

876.43 KB共4页中文简体

1天前218积分

-

璞泰来 23年受减值影响大,24Q1业绩符合预期 中泰证券 2024-04-18(4页) 附下载

璞泰来(603659)投资要点事件:公司23年实现营收153.4亿元,同比下降1%;归母净利润19....

738.89 KB共4页中文简体

1天前218积分

-

回天新材 2023年年报点评报告:原料降价拖累业绩,电子胶有望放量 国海证券 2024-04-18(12页) 附下载

回天新材(300041)事件:2024年4月16日,回天新材发布2023年报:2023年公司实现营业...

1.28 MB共12页中文简体

1天前018积分

-

九阳股份 2024一季报点评:转正见拐点 中泰证券 2024-04-18(3页) 附下载

九阳股份(002242)投资要点公司披露2024一季报:Q1收入20.7亿(+9%),归母1.3亿(...

846.24 KB共3页中文简体

1天前218积分

-

科达利 23Q4盈利水平提升,海外工厂24年有望放量 中泰证券 2024-04-18(4页) 附下载

科达利(002850)投资要点事件:公司发布2023年报,实现营收105.1亿元,同比增长21%;归...

656.31 KB共4页中文简体

1天前218积分

-

瑞芯微 业绩修复毛利企稳,关注汽车电子和AI相关布局 中国银河 2024-04-18(4页) 附下载

瑞芯微(603893)核心观点:事件公司发布2023年年报及24Q1业绩自愿性披露公告,2023年全...

396.69 KB共4页中文简体

1天前018积分

-

继峰股份 乘用车座椅龙头破局者,座椅全球替代&规模化拐点已至 中泰证券 2024-04-18(4页) 附下载

继峰股份(603997)投资要点事件:公司发布对外投资公告,为实现公司座椅全球战略,公司与控股子公司...

916.9 KB共4页中文简体

1天前218积分

-

大华股份 24Q1业绩稳定增长,多模态+中移动协同赋能长期成长空间 中泰证券 2024-04-18(3页) 附下载

大华股份(002236)投资要点事件:公司发布2023年年报及2024年一季度报告,2023年公司实...

616.7 KB共3页中文简体

1天前218积分

-

晨光生物 Q4植提加速增长,毛利率大幅承压 中泰证券 2024-04-18(4页) 附下载

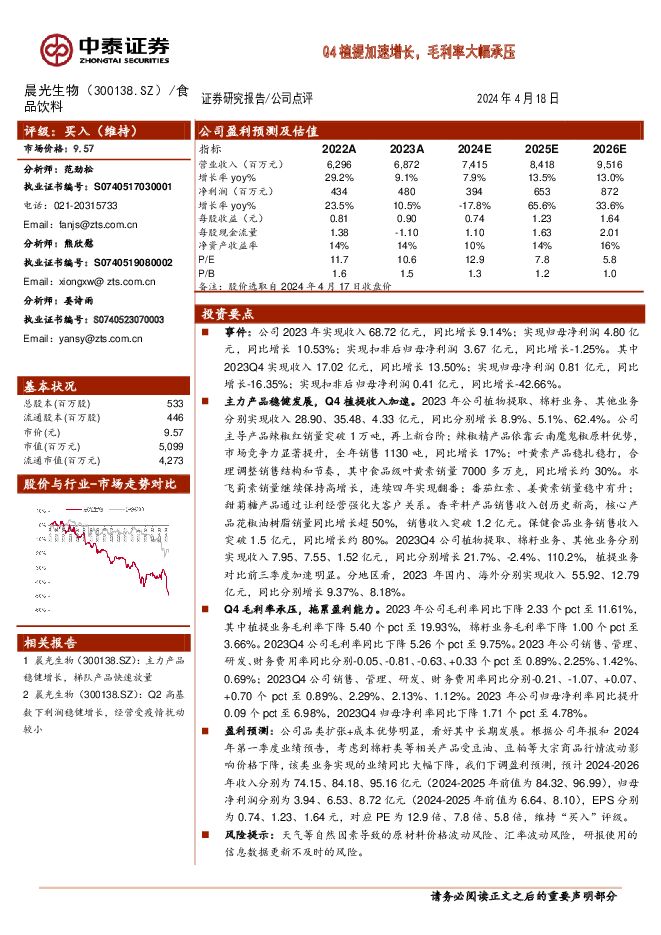

晨光生物(300138)投资要点事件:公司2023年实现收入68.72亿元,同比增长9.14%;实现...

453.25 KB共4页中文简体

1天前218积分

-

顶点软件 利润实现高速增长,把握信创机遇 中泰证券 2024-04-18(4页) 附下载

顶点软件(603383)投资要点投资事件:4月12日,公司发布2023年年度报告。2023年公司实现...

375.47 KB共4页中文简体

1天前118积分

-

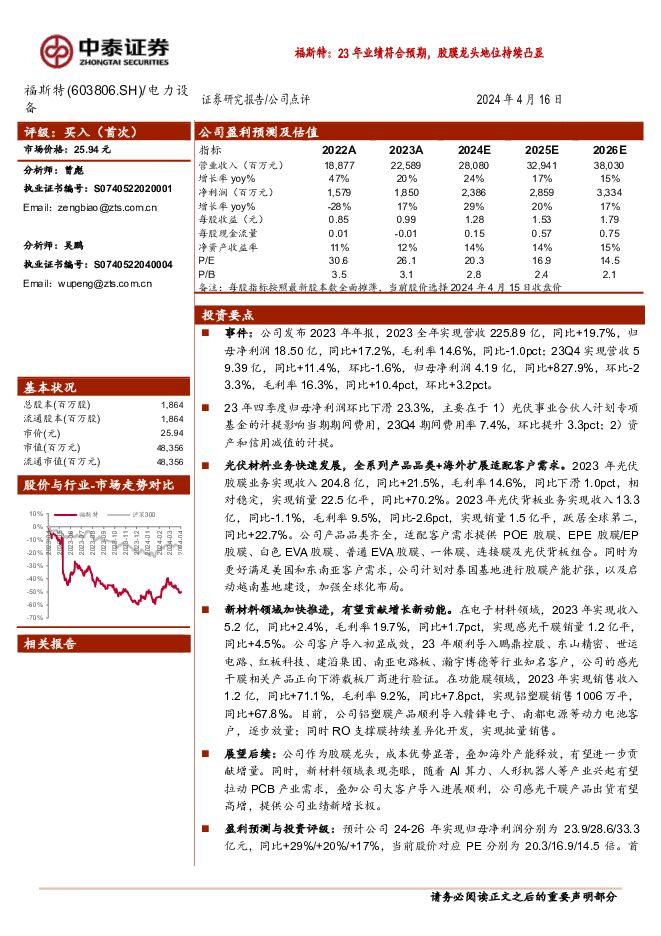

福斯特 福斯特:23年业绩符合预期,胶膜龙头地位持续凸显 中泰证券 2024-04-18(9页) 附下载

福斯特(603806)事件:公司发布2023年年报,2023全年实现营收225.89亿,同比+19....

353.85 KB共9页中文简体

1天前218积分

-

鼎龙股份 半导体材料进展顺利,业绩增长动能强劲 华金证券 2024-04-18(5页) 附下载

鼎龙股份(300054)投资要点半导体材料业务占比超30%以上,耗材业务转为盈利导向。2023年度,...

322.69 KB共5页中文简体

1天前018积分